Si dice multivibratore un circuito in grado di generare in uscita una forma d'onda di tipo rettangolare. Vi sono tre tipi di multivibratori: multivibratore monostabile

, multivibratore bistabile, multivibratore astabile.Un multivibratore si dice

monostabile quando ha un solo stato stabile, cioè normalmente l'uscita si trova a livello alto oppure a livello basso; quando arriva un impulso dall'esterno il monostabile commuta, cioè se si trovava a livello alto passa a livello basso; però finito l'effetto dell'impulso esterno, torna nello stato precedente.Un multivibratore si dice

bistabile quando ha due stati stabili, cioè normalmente l'uscita si trova a livello alto oppure a livello basso; quando arriva un impulso dall'esterno il bistabile commuta, cioè se si trovava a livello alto passa a livello basso e viceversa; finito l'effetto dell'impulso esterno, rimane nello stato determinato dall'impulso e non ritorna nello stato precedente.Un multivibratore si dice

astabile quando commuta continuamente dallo stato alto a quello basso, senza ricevere impulsi dall'esterno.Un semplice multivibratore astabile si può realizzare con le porte logiche, come nel seguente circuito:

Come si vede vi sono due porte

NOT, che danno in uscita un segnale opposto a quello ricevuto al loro ingresso, collegate in modo che l'uscita di una sia l'ingresso dell'altra.Supponiamo che all'istante iniziale il condensatore

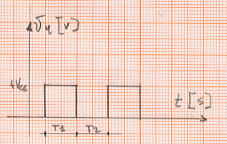

C sia scarico. Il primo NOT riceve uno zero logico in ingresso e dà in uscita sul punto B il valore 1. Il secondo NOT riceve 1 in ingresso e da in uscita zero. Il condensatore C è costretto a caricarsi, col positivo verso il basso, tramite la resistenza R2. Quando la tensione del condensatore è cresciuta fino a raggiungere il livello logico 1, sul primo NOT viene applicato il livello logico 1, tramite R1, sul punto A; sul punto B ottengo livello logico 0; in uscita ho livello logico 1. Il condensatore C è costretto a scaricarsi e caricarsi con segno opposto, cioè col positivo verso l'alto, riducendo la tensione sul punto A. Quando la tensione sul punto A raggiunge lo 0 logico, il punto B si porta a 1, e l'uscita a 0, riprendendo il ciclo iniziale. La forma d'onda in uscita sarà la seguente:

Per calcolare la frequenza, prima ci calcoliamo il periodo con la formula:

T1 = T2 = 1,1 R2 C

Dove

T1 è il tempo in cui l'uscita si mantiene a livello alto; T2 è il tempo in cui l'uscita si mantiene a livello basso.Tale formula è valida per porte logiche tipo CMOS. Poi ci calcoliamo :

f = 1

T

Il timer è un circuito integrato complesso avente lo scopo di regolare per un tempo prestabilito determinati circuiti. In pratica il timer 555 è un temporizzatore progettato dall'ingegnere svizzero

Hans R. Camenzind nel 1970. Nella seguente figura vediamo una vista esterna.

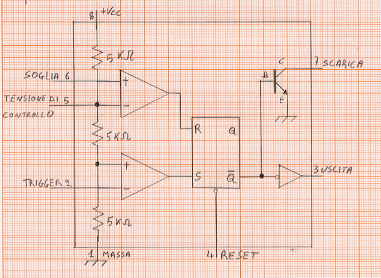

Lo schema a blocchi del circuito integrato è il seguente:

Possiamo notare tre resistori uguali da 5 k

W , aventi lo scopo di dividere la tensione di alimentazione Vcc in tre tensioni multiple di 1/3 di Vcc; in fatti tra il resistore inferiore e massa, cioè sul morsetto non invertente del secondo comparatore, abbiamo una tensione pari a Vcc/3; tra il secondo resistore e massa, cioè sul morsetto invertente del primo comparatore, abbiamo una tensione pari a 2Vcc/3; infine sul terzo resistore dal basso abbiamo tutta la Vcc. Tali tensioni ci servono come tensioni di riferimento per i due comparatori interni.Infatti vi sono due comparatori; il primo comparatore, quello superiore ha una tensione di riferimento sul morsetto invertente pari a

2Vcc/3, mentre il morsetto non invertente è disponibile all'esterno dell'integrato, sul piedino 6, detto soglia. In pratica quando la tensione sul piedino 6 è maggiore di 2Vcc/3 l'uscita del primo comparatore si porta a livello logico alto, cioè 1; quando, invece, la tensione sul piedino 6 è inferiore a 2Vcc/3 l'uscita del primo comparatore si porta a livello basso, cioè zero.Viceversa, il secondo comparatore , quello inferiore, ha una tensione di riferimento sul morsetto non invertente pari a

Vcc/3, mentre il morsetto invertente è disponibile all'esterno dell'integrato, sul piedino 2, detto trigger. In pratica quando la tensione sul piedino 2 è maggiore di Vcc/3 l'uscita del secondo comparatore si porta a livello logico basso, cioè 0; quando, invece, la tensione sul piedino 2 è inferiore a Vcc/3 l'uscita del secondo comparatore si porta a livello alto, cioè 1.Le uscite dei due comparatori sono applicate in ingresso ad un latch di tipo

S-R.Il latch di tipo S-R è un circuito logico con due ingressi e due uscite. Un primo ingresso, detto

SET, cioè porre a 1, quando si trova a 1, obbliga l'uscita Q a portarsi a 1; il secondo ingresso, detto RESET, cioè azzerare, quando si trova a livello logico 1, porta l'uscita Q a zero, cioè l'azzera. La tabella di verità è la seguente:

E' un corso a pagamento dal costo di 3 € per 365 giorni.

Sono gratuite le seguenti lezioni:

Indice di tutte le pagine del sito