Se dice multivibrador un circuito capaz de generar una forma de onda de salida de tipo rectangular. Hay tres tipos de multivibradores. Multivibrador monoestable, multivibrador biestable, multivibrador astable.

Un multivibrador se dice monoestable cuando se tiene sólo un estado estable, que es normalmente la salida es a un nivel alto o un nivel bajo; cuando un impulso llega desde fuera el monoestable conmuta, es decir, si estaba en un nivel alto pasa a bajo nivel; sin embargo, el efecto de pulso finito externo, de vuelta a su estado anterior.

Un multivibrador se dice biestable cuando ha dos estados estables, que es normalmente la salida está en un nivel alto o un nivel bajo; cuando un impulso llega desde fuera el biestable conmuta, es decir, si estaba en un alto nivel pasa a bajo nivel y viceversa; sobre el efecto del impulso externo, permanece en el estado determinado por el impulso.

Un multivibrador se dice astable cuando constantemente conmuta de nivel alto a nivel bajo, sin recibir impulsos desde el exterior.

Un multivibrador astable sencilla se puede realizar con las puertas lógicas, como en el siguiente circuito:

Como se puede ver hay dos puertas NOT, que dan una señal de salida opuesta a la que recibe en su entrada, conectados de manera que la salida de un sea la entrada de la otra.

Supongamos que en el instante inicial el condensador C

Como se puede ver hay dos puertas NOT, que dan una señal de salida opuesta a la que recibe en su entrada, conectados de manera que la salida de un tanto la entrada de la otra.

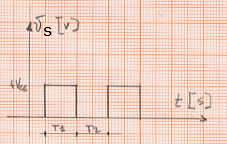

Supongamos que en el instante inicial el condensador C sea descargado. El primero NOT recibir una entrada de cero lógico y da en salida en el punto B el valor 1. El segundo NOT recibe 1 en la entrada y da en salida cero. El condensador C se ve obligado a cargar, con el positivo hacia abajo, a través de la resistencia R2. Cuando la tensión del condensador ha crecido hasta alcanzar el nivel lógico 1, en el primero NOT se aplica el nivel lógico 1, a través de R1, en el punto A; en el punto B obtengo el nivel lógico 0; en salida he nivel lógico 1. El condensador C se ve obligado a se descargar y cargar con el signo opuesto, es decir, con el positivo hacia arriba, reduciendo la tensión en el punto A. Cuando la tensión en el punto A llegue a el 0 lógico, el punto B se lleva a 1, y la salida a 0, recuperando el ciclo inicial. La forma de onda de salida será como sigue:

Para calcular la frecuencia, primero calculamos el período con la fórmula:

T1 = T2 = 1,1 R2 C

Donde T1 es el tiempo en el que la salida se mantiene a alto nivel; T2 es el tiempo en el que la salida se mantiene en el nivel bajo.

Esta fórmula es válida para puertas lógicas CMOS. Entonces calculamos:

f = 1

T

El temporizador es un circuito integrado complejo que tiene el propósito de ajustar por un tiempo determinado circuitos predeterminados. En la práctica, el temporizador 555 es un circuito temporizador proyectado en el 1970 por un ingeniero nacido en Suiza Hans R. Camenzind. En la siguiente figura podemos ver una vista exterior.

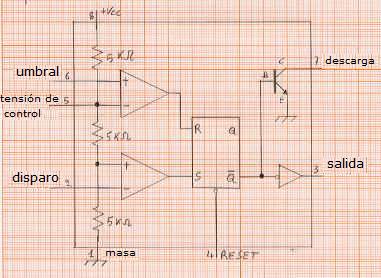

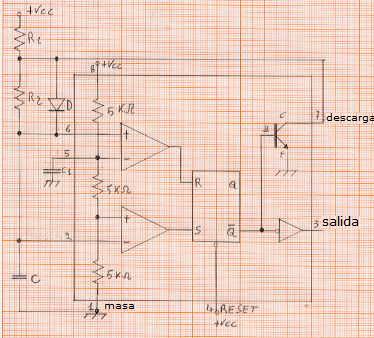

El diagrama de bloques del circuito integrado es la siguiente:

Observamos tres resistores iguales de 5 kW, que tienen el propósito de dividir la tensión de alimentación Vcc en tres tensiones múltiples de un tercio de Vcc; en los hechos entre la resistor inferior y la masa, es decir en el terminal no inversor del segundo comparador, tenemos una tensión igual a Vcc/3; entre el segundo resistor y la masa, es decir en el terminal inversor del primer comparador, tenemos una tensión igual a 2Vcc/3; por último, en el tercero resistor de la parte inferior tenemos toda la Vcc. Estas tensiones nos sirven como tensiones de referencia para los dos comparadores internos.

De hecho, hay dos comparadores; el primer comparador, el superior tiene un tensión de referencia en el terminal inversor igual a 2Vcc/3, mientras que el terminal no inversor está disponible fuera del circuito integrado, en la patilla 6, dicha umbral. En la práctica, cuando la tensión en la patilla 6 es mayor que 2Vcc/3 la salida del primer comparador va a un nivel lógico alto, es decir 1; cuando, en vez, la tensión en la patilla 6 es menor que 2Vcc/3 la salida del primer comparador pasa a un nivel bajo, es decir, cero.

Por el contrario, el segundo comparador, el inferior, tiene una tensión de referencia en el terminal no inversor igual a Vcc/3, mientras que el terminal inversor está disponible fuera del circuito integrado, en la patilla 2, dicha disparo. En la práctica, cuando el tensión en la patilla 2 es mayor que Vcc/3 la salida del segundo comparador va a un nivel lógico bajo, es decir, 0; cuando, en lugar, la tensión enla patilla 2 es inferior a Vcc/3 la salida del segundo comparador pasa a un nivel alto, es decir, 1.

Las salidas de los dos comparadores se aplican a la entrada de un latch tipo S-R.

El tipo latch S-R es un circuito lógico con dos entradas y dos salidas. Una primera entrada, dija SET que se pone a 1, cuando está a 1, obliga a la salida Q para mover a 1; la segunda entrada, dicha RESET, es decir anulación, cuando está en nivel lógico 1, lleva la salida Q a cero, es decir, se restablece. La tabla de verdad es la siguiente:

|

S |

R |

Q |

Q |

| 0 | 0 | Q | Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 |

indeterminado |

indeterminado |

En el temporizador 555 de las dos salidas la salida Q no se usa, pero se usa sólo la salida Q negada. Si Q negada es en el alto nivel, envía el transistor en saturación, y luego la patilla 7 está conectada a masa, lo que permite la descarga de un condensador, que normalmente se aplica a la patilla 7; pero si la salida Q negada es a un nivel bajo, el transistor se inhibe, entonces la patilla 7 está aislado de masa, permitiendo la carga del condensador. En en la salida Q negada se aplicaun inversor, que convierte la salida Q negada en la salida Q, y también permite una alta corriente de salida. El temporizador 555 puede ser utilizado tanto multivibrador astable como, que como biestable.

MULTIVIBRADOR ASTABLE CON TEMPORIZADOR NE 555

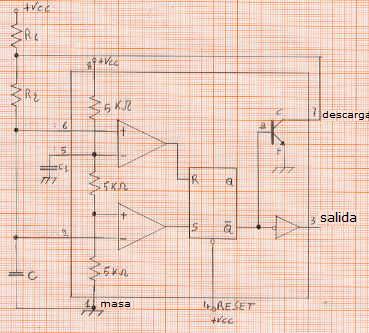

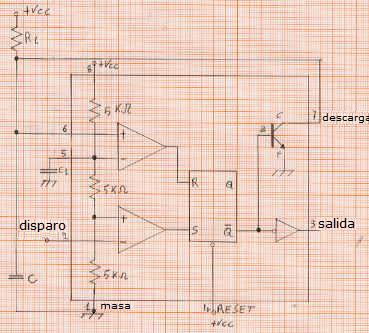

El multivibrador astable es un circuito capaz de generar una forma de onda rectangular, sin señal aplicada en la entrada. El esquema es el siguiente:

Supongamos que inicialmente el condensador C sea descargado, las entradas de los dos comparadores en las patillas 2 y 6 se encuentran en bajo nivel; el comparador superior da en salida un nivel bajo, entonces R = 0; el comparador inferior da en la salida un nivel alto, entonces S = 1; el latch S-R pone la salida Q a 1, mientras que Q negado = 0; la salida del temporizador en el la patilla 3 es de alto nivel; el transistor se inhibe, porque la base no es directamente polarizada, la patilla 7 está aislado de la masa, el condensador C comienza a cargarse a través de los resistores R1 y R2 que están en serie.

Cuando la tensión a los bornes del condensador C alcanza el valor de Vcc/3, el comparador inferior conmuta y se lleva a nivel bajo, S = 0; el latch S-R no conmuta porque incluso R = 0, y luego la parte restante del circuito permanece en el estado anterior, y el condensador mantenga a se cargar. Cuando la tensión a los bornes del condensador C alcanza 2Vcc/3 entonces el comparador superior conmuta, con lo que su salida de alto nivel, R = 1; el latch S-R restablece su salida Q; Q negado = 1; la salida del integrado es a bajo nivel; se satura el transistor, poniendo la patilla 7 del temporizador a masa; el condensador se ve obligado a descargar a través de el resistor R2 solamente.

Cuando la tensión del condensador C cae por debajo de Vcc/3 entonces el comparador inferior conmuta, llevando S a 1, mientras que R ya estaba en cero sólo iniciado la descarga; entonces el latch S-R que tiene S=1 lleva su salida Q a 1, y Q negado a 0; la salida del temporizador va a un alto nivel; el transistor está prohibido, la patilla 7 se separa de la masa, el condensador comienza a cargarse, repitiendo el ciclo anterior.

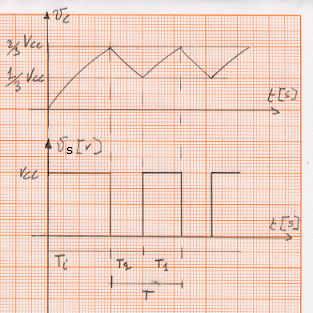

Los diagramas son los siguientes:

Sin tener en cuenta el tiempo de carga inicial de Ti, en el que el condensador parte de tensión cero, denotamos por T1 el tiempo en el que la salida se mantiene a nivel alto, y el condensador se está cargando; T1 se puede calcular con la siguiente fórmula:

T1 = 0,693 (R1+R2) C

De hecho, el condensador se carga a través de R1 y R2.

Denotamos por T2 el tiempo en que la salida se mantiene en el nivel bajo; T2 se puede calcular con la siguiente fórmula:

T2

= 0,693 R2 CSumando las dos veces T1 y T2 obtenemos todo el período que se

T = T1 + T2

La frecuencia es la inversa del periodo, es decir,

f = 1

T

Se dice ciclo útil D la relación entre T1 y T, es decir,

D = T1

T

Observamos que es difícil obtener un ciclo útil de 50%, es decir, T1 = T2, que es el tiempo en el que la forma de onda está en el alto nivel es igual al tiempo en el que la forma de onda es a bajo nivel; para lograr esto debemos poner R2 = 0; sin embargo R2 es la resistencia del colector del transistor interno, que no puede tener valores de menos de 1000 W, para evitar quemar el transistor. Para obtener R2= 0 se puede poner en paralelo a R2 un diodo, de acuerdo con el siguiente esquema:

de esta manera durante la carga del condensador C, el diodo D es polarizado directamente y se comporta como un corto circuito, el condensador se carga sólo a través de R1; durante la descarga del condensador, el diodo es polarizado inversamente, por lo que es como un circuito abierto, lo que permite que el condensador se descargue a través de R2.

El condensador C1 sirve como una nivelación de la tensión de referencia. El terminal de RESET debe estar conectado a + Vcc, así como para excluirlo.

MULTIVIBRADOR MONOESTABLE CON TEMPORIZADOR 555

El multivibrador monoestable genera una forma de onda rectangular en la salida, sin embargo necesita de un impulso externo por ser capaz de la generar. El esquema es el siguiente:

El monoestable tiene un sólo estado estable, en nuestro caso, la salida se mantiene siempre en un nivel bajo hasta que se recibe un impulso desde el exterior, en la patilla 2. De hecho, el mantenimiento de un alto nivel en la patilla 2, el comparador inferior da en la salida un valor bajo; entonces S=0; en lugar el comparador superior, el condensador siendo inicialmente descargado, da en salida 0; entonces R=0; a continuación, el latch S-R permanece en la condición de reposición, es decir, Q=0; Q negado = 1; la salida del temporizador es cero; el transistor pasa a saturación, siendo la base polarizada directamente, la patilla 7 está conectada a masa, y el condensador C no puede cargar a través del resistor R1. El circuito es estable con salida de nivel bajo.

Cuando llega un impulso desde el exterior en la patilla 2, dicha disparo, la tensión en el patilla 2 es forzada a cero, el comparador inferior da en salida un nivel alto; S=1; mientras que R se mantuvo en 0; inmediatamente a la salida Q del latch S-R va a 1, mientras que Q negado = 0; la salida del temporizador pasa a 1; el transistor se inhibe, el condensador comienza a cargarse a través de el resistor R1; cuando la tensión en el condensador alcanza 2Vcc/3 el comparador superior conmuta llevando la salida a en alto nivel, entonces R=1; mientras que el comparador inferior ya ha dado la salida de nivel bajo cuando el condensador ha excedido Vcc/3; entonces S=0; la salida del latch S-R se restablece, entonces Q=0; Q negado = 1; la salida del temporizador va a un nivel bajo; el transistor va a la saturación descargando el condensador.

El condensador C1 sirve como una nivelación de la tensión de referencia. El terminal de RESET debe estar conectado a + Vcc, así como para excluirlo.

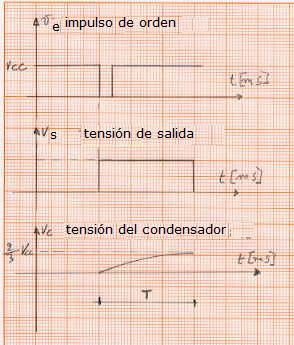

Los diagramas son los siguientes:

Denotemos por T el tiempo en el que el condensador se carga, se tiene que:

T = 1,1 R1C

2014

|

|

|

Indice de todas las páginas del sitio